- 发布时间:2022/1/14 来源:深圳市铨祺科技有限公司

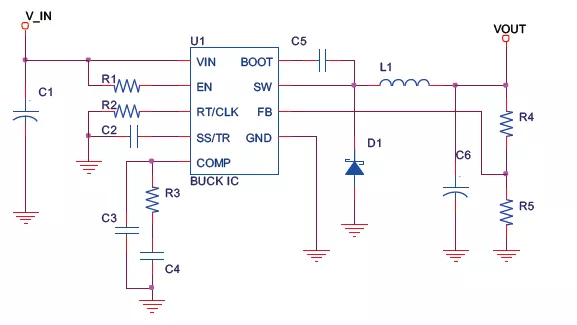

一.Buck电路

Buck电路如下图

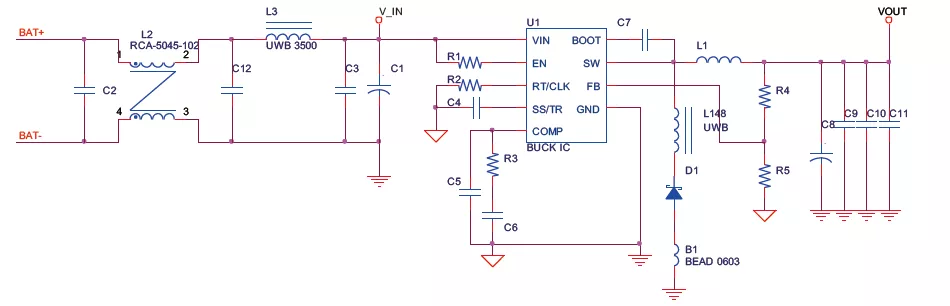

增加EMC对策后如下图

-

在输入端增加L2,L3搭配电容形成的共差模滤波器。L3,C1,C3,C12可以有效抑制开关电源所造成的EMI杂讯,此处的元件挑选需针对开关电源主频频率来设定。L2可以抑制因板端Layout不良而造成的共模杂讯,同时L2也是个有效解决EMC的元件(BCI 7637&RS)

-

于Diode A 脚串接Ferrite Bead 600 ohm并在Diode的C脚串接UWB3500,此对策可有效抑制Diode因Mos开关而产生反向电流的状况。

-

Layout上必须注意由BUCK回路需要越小越好,PGND与AGND需单点连接。

-

电源问题通常来自于不专业的Layout规划造成许多共模杂讯干扰,在此,L2为一个选择性的对策。

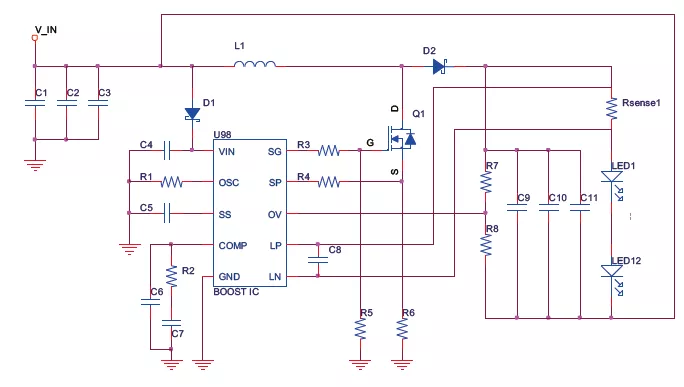

二.Boost To GND B2G电路如下图

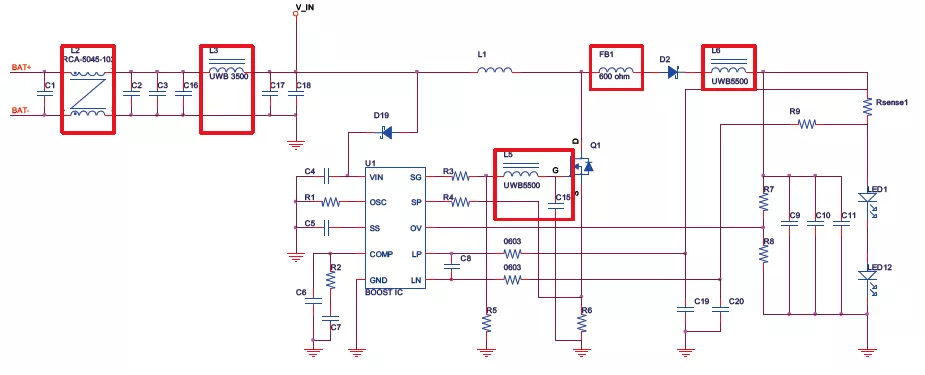

增加EMC对策后如下图

-

在输入端增加L2,L3搭配电容形成的共差模滤波器。

L3,C2,C3,C12,C13,C14可以有效抑制开关电源所造成的EMI杂讯。此处的元件挑选需针对开关电源主频频率来设定。

L2可以抑制因板端Layput不良而造成的共模杂讯,同时L2也是个有效解决EMS的元件(BCI 7637&RS)

-

于Q1 Gate脚增加UWB3500搭配接地电容的LC电路来抑制因Q1开关而产生的高频问题,藉由LC电路来修正VGS上升及下降的波型,因UWB直流阻抗小的特性,此电路并不会增加MOS功率损耗(电容过大还是会影响功率)。

-

于Diode的A脚串接Ferrite Bead 600ohm并在Diode的C脚串接UWB3500,此对策可有效抑制Diode因Mos开关而产生反向电流的状况。

-

Layout上必须注意GND的走线方式,BOOST的回路必须做小,PGND与AGND需单点连接。R sence回到LP,LN脚的走线请平行走线,且必须由R sense两PIN单独走回BOOST IC

-

电源问题通常来自于不专业的Layout规划造成许多共模杂讯干扰,在此,L2为一个选择性的对策。

整合型电源问题:

在多电源产品设计中,通常电源都是来自于下列几个问题而产生:

1.不良机构的设计

散热片接地或直接使用外壳散热问题:

金属制散热片若使用在开关电源的功率元件上(ex.L,D,Q),散热片必须接到功率地上,并透过导热矽胶片与外壳连接。

禁止直接使用外壳触碰电感及Mos散热

禁止直接使用导热矽胶片与外壳连接

产品内部线束布局错误:

线束乱飞

高速排线未屏蔽

线束直接触碰板上高速或电源电路元件

线束上地回路任意相接

外壳接地问题:

没有外壳地(意即外壳地及信号地)

板上地回路透过外壳掠过滤波器

外壳为阳极处理

连接器布局错误:

高低速连接器交错(或是Top/Bottom相叠)

高地压连接器太近

线束设计问题:

任意将电源地与参考地、屏蔽地或其它不知名的地相接

线材内部包覆错误

2.错误的PCB布局规划

主电源电路远离端口或滤波器

高低速信号交错

类比/数位电源地未分离

上述问题基本上都是常识,但若因空间问题(2D或3D)导致上述问题的产生,端口必须增加滤波器(依杂讯频率选用元器件),板层走线要想办法错开高低速信号。类比/数位则必须依靠Layout技巧达成单点接地。

3.电源单体电路不专业的Layout走线

-

没有功率布线

-

功率回路中穿插类比甚至数位信号走线

-

功率元件正反面交错摆件

-

地回路过大或阻抗过高

-

多层板的应用错误

-

元件下错地

上述的问题是最常见的Layout问题,通常都是在上述行为造成板上出现极大的共模信号,也通常都反映在传导76-108Mhz,辐射142-245Mhz。若是2.2Mhz的主频,在300-400Mhz也会出现。建议多看看IC Spec上的建议Layout方式,Layout应该以功率地为主。

4.端口滤波设计错误

-

没有滤波元件,基本上不管是多大的厂商,所有电源IC的基础电路在裸板的情况下都是过不了车规的,建议尽量预留一些滤波元件。

-

滤波元件选用错误,必须充分了解干扰源的杂讯,再依目标频率选择正确的Inductor/Bead/Capacitor

-

元器件摆设位置不正确,通常是发生在信号线端口处的TVS或电容等元器件,通常都是反映在BCI跟RS这两个EMS的测试项目。也会反映在一些比较特殊的测试项目。某些车厂会要求测试信号线的传导(ex.Toyata TSC0505)。

会发生这个问题通常是地回路有极大的问题:

BCI/RS:元器件接地点为某个类比的参考地(或是可以解释成类比的参考地跟元器件的地未分离或阻抗太小)

EMI:接地点上的杂讯透过元器件传导到信号线上,这个在排查上要花很多时间,但是解决办法往往很简单,换个地接就好。

-