- 发布时间:2022/1/14 来源:深圳市铨祺科技有限公司

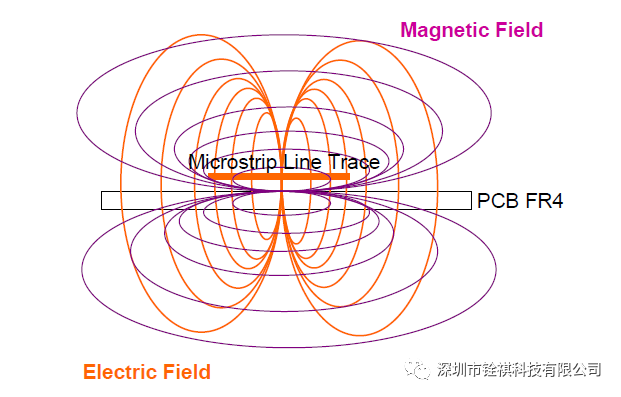

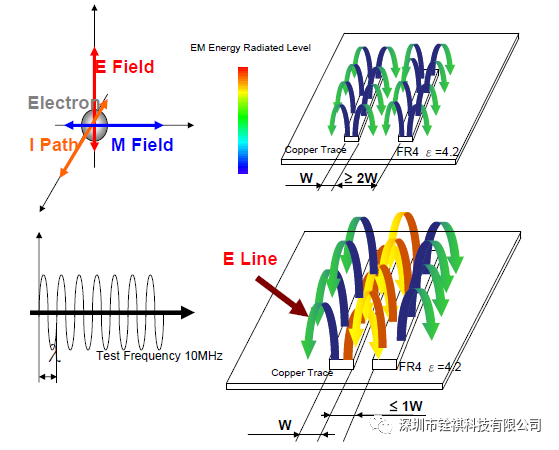

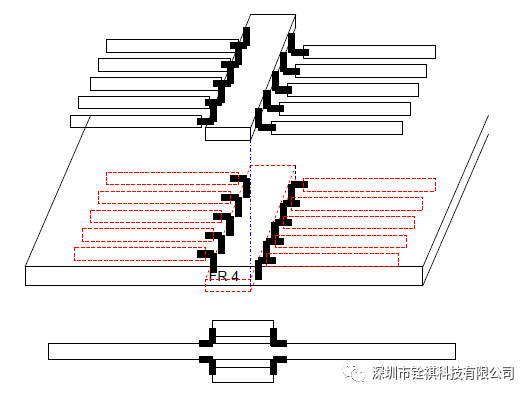

微带线电磁场辐射模型

走在PCB最外层的铜质信号传输线又称为微带线,因为走线裸露在PCB最外层,上面没有金属介质遮蔽,所以当通电以后电流及电压在走线上快速流动所形成的电场及磁场会直接辐射出来。

与走线平行的辐射场为磁场(Magnetic Field)

与走线垂直的辐射场为电场(Electric Field)

PCB低电磁波辐射布线原则

布线宽度:地线>电源线>信号线

从低电磁波辐射设计的观点来考量布线的原则,一般而言设计者必须让整块PCB处于一个高频低阻抗的理想状态,而布线的宽度越宽,高频的阻抗会越低,所以PCB的地面积越大则高频阻抗与感抗都会越低。

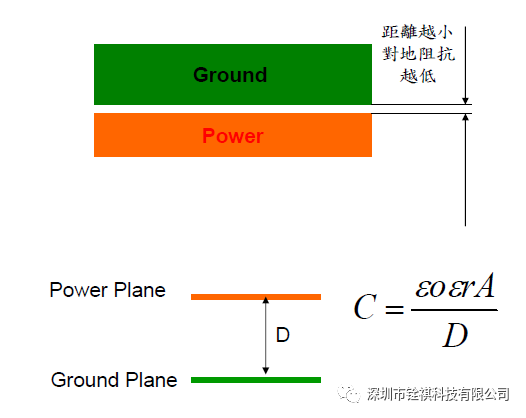

电源线:在考虑安全状况下,电源线尽可能靠近地线,以增加两线之间的电容性,藉此可降低两线之间的对地阻抗,减小差模辐射的环路面积,也有助于减小电路的串音干扰。

上图可看作为一个电容,电源层和地层是电容的2个极板。极板的距离越近,电容越大则阻抗越低,如此可以减低EMI Noise。

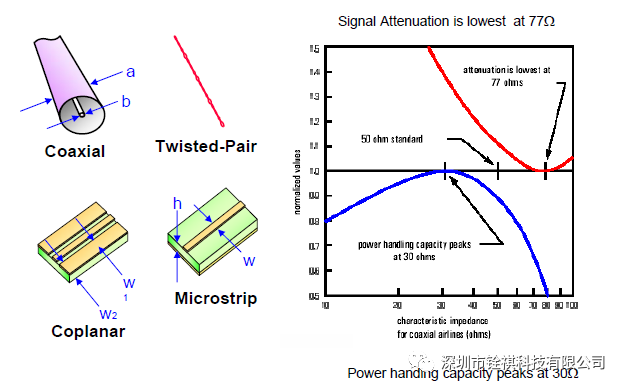

传输线理想阻抗Z0

如果有一种传输线可以让信号传输损失最小,功率传输效益最大,那种传输媒体就必须具备最理想的传输阻抗Z0,来实现这样理想的传输特性。

由下图得知传输线的信号传输损失最小的理想阻抗约为77Ω,功率传输效益最大的理想阻抗约为30Ω,两者并没有交集点,因此只好将两者相加除以2取其平均近似值50Ω做为Z0.

理想的传输线没有反射,没有杂讯。

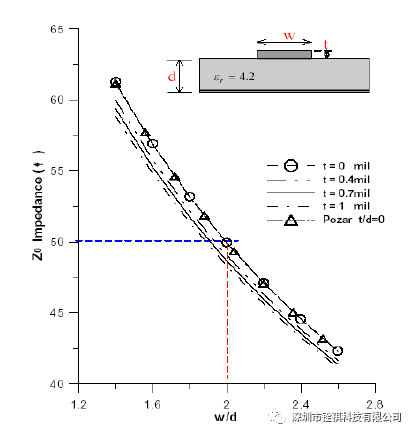

如何使走线实现理想的50Ω传输阻抗特性,由下图得知,如果把一条铜线走在RF4的PCB板材上,则线宽(W)比线至最近参考面的距离(d)为2:1的比例时,此时这条走线便具有最接近理想的50Ω(Z0)传输阻抗特性。

如何使走线实现理想的50Ω传输阻抗特性,由下图得知,如果把一条铜线走在RF4的PCB板材上,则线宽(W)比线至最近参考面的距离(d)为2:1的比例时,此时这条走线便具有最接近理想的50Ω(Z0)传输阻抗特性。

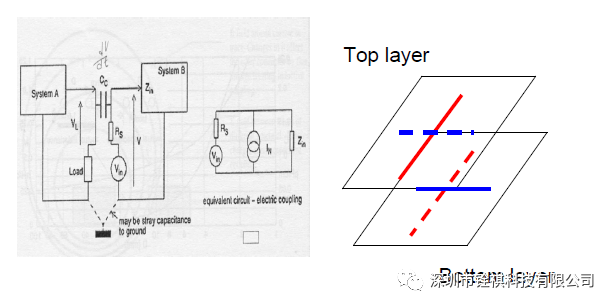

电场(电容性)耦合感应

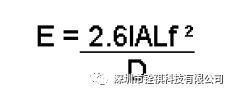

电容性耦合(dv/dt):两导线以上下正交方式耦合面积最小。由线与线(同层或不同层)间所引起的串音等耦合效应均会形成差模干扰。

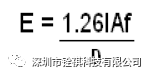

电场(电容性)耦合感应:差模干扰效应

电场(电容性)耦合感应:差模干扰效应

(I:布线电流 A:布线(交错/叠合)面积 L:布线长长 f:信号工作频率 D:线间距离)

以上微带线模型案例纯属线与线之间的耦合所引发的差模杂讯场效应皆不考虑回返电流路径面积的考量。

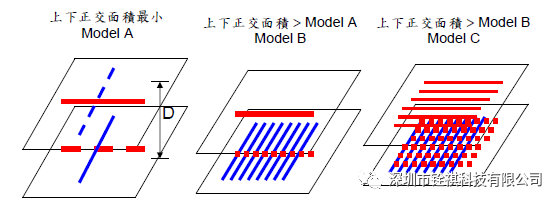

2平行微带线的电场耦合模拟模型

依据3W的设计理论推导,两条平行线的线距刚好大于或等于两倍线宽的时候,这两条平行线所辐射的电磁场不会互相耦合。

在布线的原则中,两条平行线的串音耦合结果会导致线对线的差劲杂讯辐射是最严重的.

下图所示的IC输入输出端的导线上下层完全重叠且平行,对电磁波辐射而言是最差的状态。

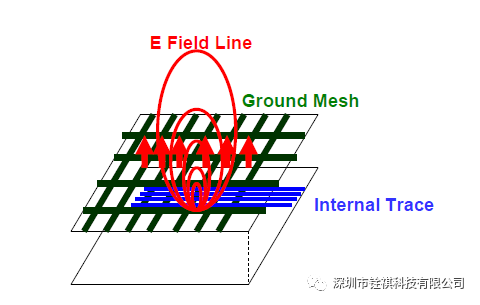

网格状地线对电磁辐射的影响

采用栅极格状接地,对电磁波没有遮蔽性,内层传输线的电磁波会直接从非金属介质的空隙穿透,故以低辐射的PCB Layout设计而言,不建议使用网络状接地。

可避免大面积铜箔面积因长期受热发生的膨胀与脱落利于排除铜箔与基板黏合剂受热产生的挥发性气体。

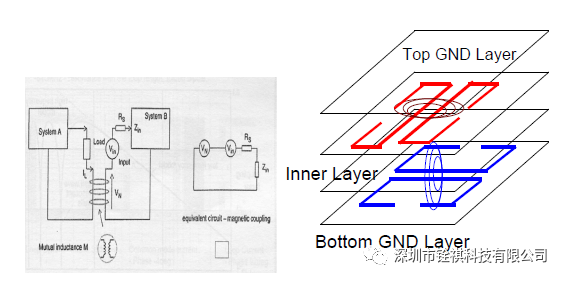

磁场(电感性)耦合感应

电感性耦合(di/dt)以多层板堆叠方式(Multilayer stack-up)降低磁通量

磁通量:由电子流的原子核运动产生的微小电流所形成。

共模干扰(场效应强度)

(I: 回路电流 A:回路面积 f:工作频率 D:回路距离)

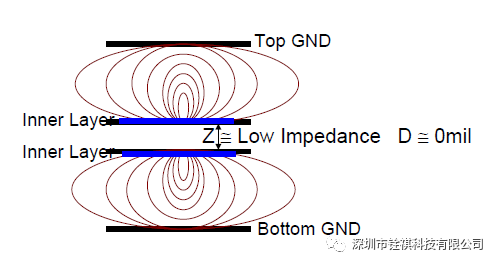

带线(strip Line)场模型

内层带线场形会被外层GND层覆盖无法穿透而受到压迫变形结果使外层场辐射变小。

所以从低电磁波辐射设计的观点来进行Layout的设计应尽可能的将时钟信号线及高速的数位汇流排线及蛇线等高辐射的走线,走在内层以降低走的线在表层的辐射。

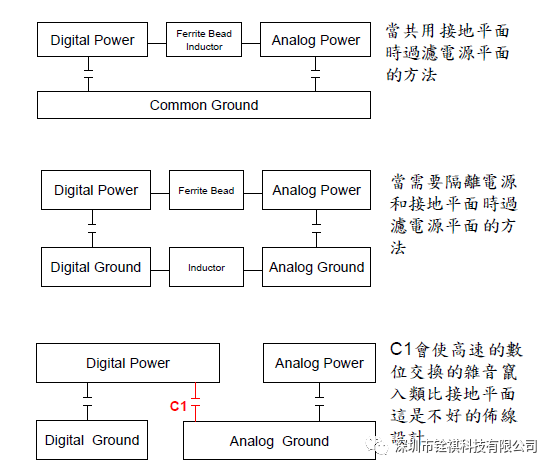

接地与电源平面分割的方法

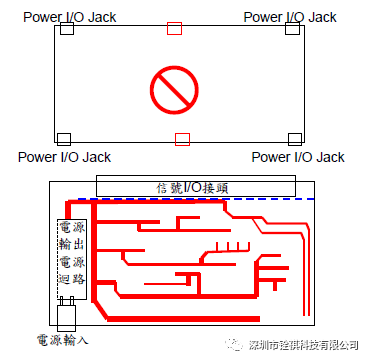

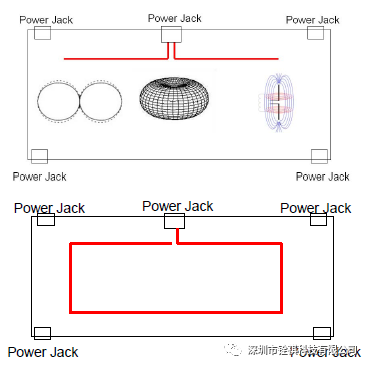

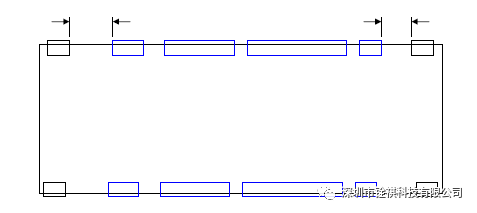

以产品良好EMC设计观点而言,电源输入端位置最好安排在产品的四个角落,尽量避免置放在产品中间位置,并且将电源走线以树枝状分散分布于PCB上。

如果产品的电源输入端位置在中间则容易形成对称振子天线效应,或者容易形成环状天线效应,都很容易将电磁波直接辐射出去。

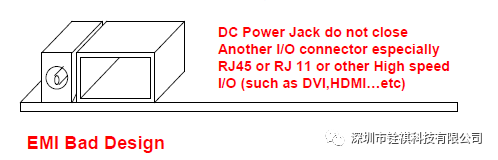

产品的电源输入端子最好与高速数位信号端子保持一定距离,不要紧贴在一起。

如果电源供应端子与高速数位信号端子紧贴在一起的时候,当电源线及高速数位信号线插上端子接口后,其PCB内部的电磁杂讯会透过端子接口将杂讯串入信号线及电源线,此时端子外部的电源线与信号线距离太近,会直接产生线对线的信号耦合干扰效应,导致EMC测试失败。

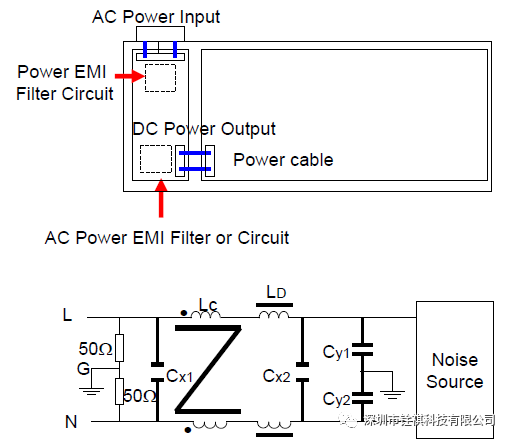

产品的交流电源输入区块由其在一侧区块必须有基本交流滤波回路设计,以确保该电源的低频宽带杂讯有滤波的处理。

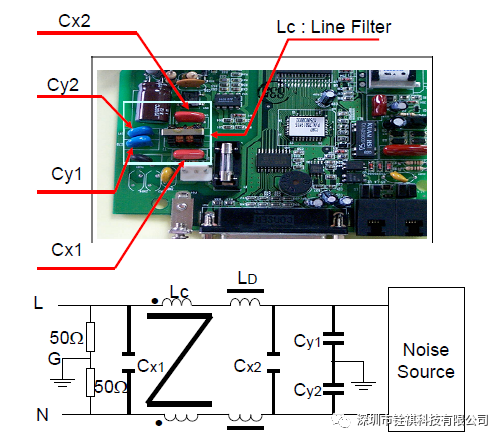

常用之交流电源供应滤波回路架构

照片所示为基本交流电源供应的滤波回路组态

Cy:Y电容 Cx:X电容 Lc:共模滤波器

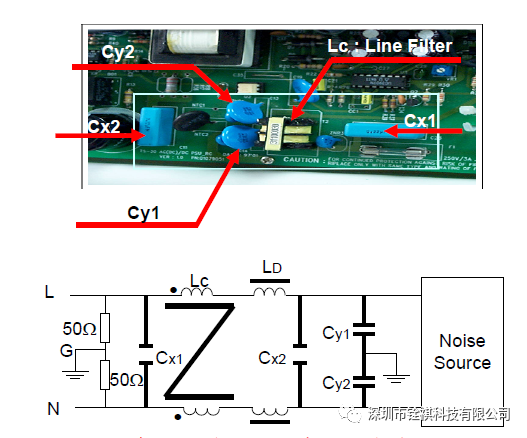

常用之交流电源供应滤波回路架构

照片所示为基本交流电源供应的滤波回路组态。

Cy:Y电容 Cx:X电容 Lc:共模滤波器

常用之交流电源供应滤波回路架构

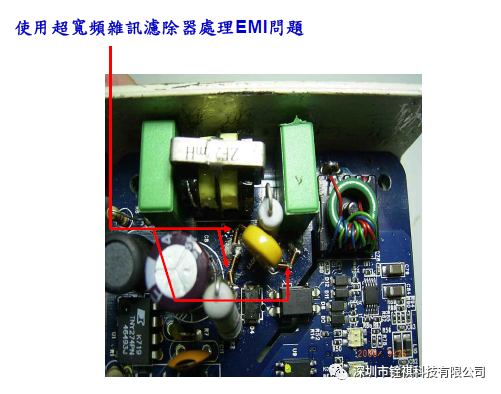

浮接式(AC Floating)交流电源供应滤波回路

照片所示POE电源供应的回路架构,因为POE的架构为2Pin,没有接地Pin脚的浮接式交流(AC Floating)电源供应系统,所以对地的共模杂讯无法使用Y电容滤除,因此在一次侧的火线(Line)及中性线(Neutral)路径上必须加入超宽频(UWB Noise Filter)杂讯滤除器来将电源线的杂讯滤干净。

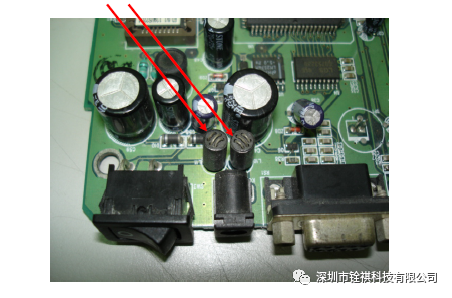

直流电源供应回路滤波

早期的直流式电子产品因为产品内部的工作频率低,所以大都使用DC Choke(俗称猪鼻子)放在直流电源供应输入端,来滤除低频的电源杂讯。

直流电源供应回路滤波

今日的直流式电子产品因为产品内部的工作频率变快变高,所以使用DC Choke放在直流电源供应输入端,来滤除低频的电源杂讯己无法满足电源杂讯滤波的需求,因为电源处理IC的交换信号很快速,所以产生的电磁辐射杂讯频带也变的更宽,因此需使用超宽频杂讯滤波元件来完成电源杂讯的滤波。